5月3日下午,王彪博士受邀为微纳电子学系同学进行线上讲座,王博士向我系师生就他的研究思路及主要工作进行了介绍和分享。

本次报告由祁亮老师主持,祁老师介绍了王博士的学习工作经历及主要研究领域,并对王博士表示了欢迎,随后王博士向我系师生就增量式sigma-delta 模数转换器的特性,重点展示了他博士期间的研究思路以及成果。

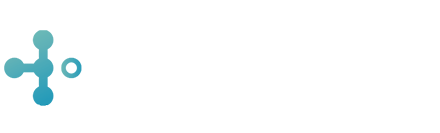

王彪博士从研究背景出发,提出了在模拟前端信号采集应用领域,以耳机采集,低速高精度音频应用为主的模数转换器,大部分面积被电容阵列占据的问题,而增量式ADC凭借其多路共用性能更具优势。王博士进一步介绍了增量式ADC与传统sigma-delta ADC相比,具有数字滤波器简化,时序延时变短,更适用于多通道测量,消除低频idle tone等优势;但在KT/C噪声,多比特量化器DWA处理方面仍存在一些挑战。

王博士首先以一阶增量式ADC为例,对增量式ADC的系统工作原理和传递函数进行了理论讲解,并进一步拓展到多阶积分器级联结构的精度计算,以及累加权重不均匀对高阶增量式ADC热噪声影响的分析。

之后王博士介绍了二阶增量式ADC的改进DEM算法,和三阶增量式ADC第一积分器分层技术两个先进工作,分析了其优势与缺陷,并指出了增量式ADC与传统sigma-delta ADC的研究重点有很大的不同。并在此结论的基础上重点展示了他博士期间的研究思路以及成果。

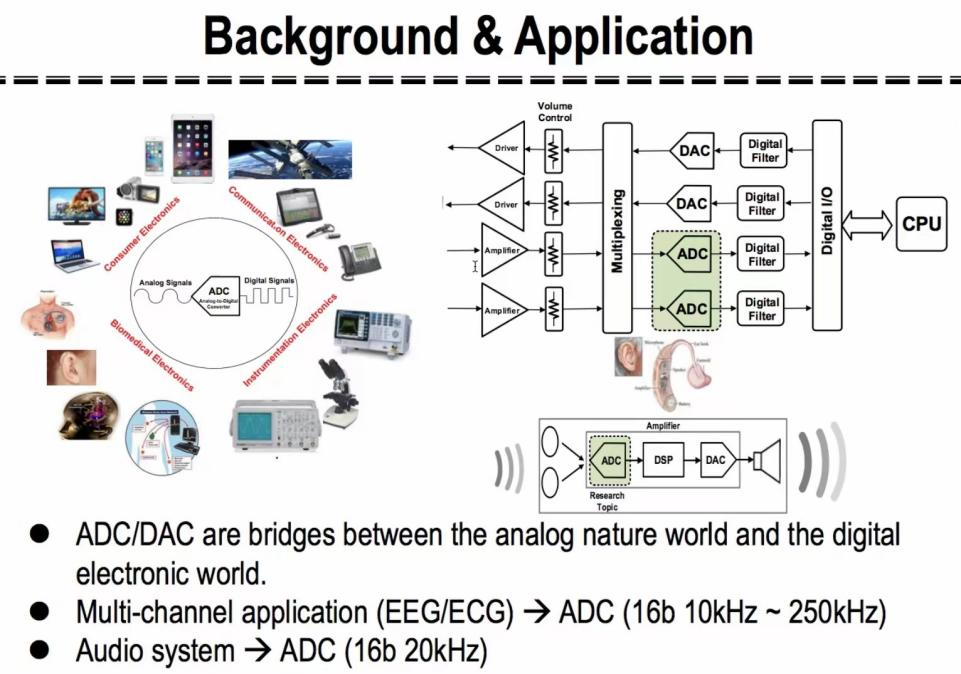

在这一部分,王博士首先基于对增量式ADC mismatch error权重的分析,提出了1.5+7bits 分段反馈DAC 技术。在第二个工作中,王博士分别通过噪声耦合技术,和正反馈积分器实现增量式ADC指数累加,并为解决ORS降低KT/C噪声同DWA失效的问题,介绍了线性——指数累加架构的解决方案,应用于低速高精度、高速高精度的两个主要案例。

王博士的报告详细清晰,内容丰富,干货满满,形象地分享了自己在增量IADC研究中“成也权重,败也权重”的研究思路和优秀经验!会后,老师同学们就报告相关内容提出了一些问题,并与王博士进行了更深入的讨论,王博士也给予了耐心细致的解答。参与报告会的师生均表示受益匪浅!

王博士简介: 王彪,本科毕业于西安电子科技大学,硕士毕业于复旦大学,并于澳门大学获得博士学位。博士毕业后进入业界,主要从事于模拟集成电路设计工作, 涉及但不限于ADDA、PLL、收发机链路。王彪博士, 在博士期间以第一作者身份在集成电路设计领域顶级期刊与会议发表多篇论文,包括1篇JSSC, 1篇VLSI, 一篇ASSCC以及一篇prime。他担任IEEE Journal of Solid State Circuit, IEEE transactions on circuits and system I 等期刊的审稿人。他并于2016年获得prime 会议 “银叶子”论文奖以及IEEE电路与系统会议奖学金。他拥有一项美国专利。

附:与王博士本次讲座相关的论文

1.B. Wang, et al., “A 1.2V 86dB SNDR 500kHz BW Linear-Exponential Multi-Bit Incremental ADC Using Positive Feedback”, ASSCC 2019.

2.B. Wang, et al., “A 550-μW 20-kHz BW 100.8-dB SNDR Linear-Exponential Multi-Bit Incremental SD ADC with 256 Clock Cycles in 65-nm CMOS,” in IEEE Journal of Solid-State Circuits, vol. 54, no. 4, pp. 1161-1172, Apr. 2019. (Invited)

3.B. Wang, et al., “A 550mW 20kHz BW 100.8dB SNDR Linear-Exponential Multi-Bit Incremental Converter with 256-cycles in 65nm CMOS,” in IEEE Proc. Symp. VLSI Circuits, Jun. 2018.

4.B. Wang, et al., “A High-Resolution Multi-Bit Incremental Converter Insensitive to DAC Mismatch Error,” in IEEE Proc. Ph.D. Research in Microelectronics and Electronics (PRIME), pp.1-4, June 2016. (Silver Leaf Award)