2024年4月21日到24日,集成电路设计领域顶会之一的IEEE定制集成电路大会(CICC)在美国科罗拉多州丹佛市举行。在本届CICC上,上海交通大学微纳电子学系生物电路与系统实验室(BiCASL)有2篇高水平论文入选,向国际集成电路设计领域的同行展示了BiCASL最新的研究成果。这两篇论文内容涉及高精度模数转换器芯片、生理信号采集前端芯片这两个学术前沿领域。论文的详情如下:

1. 高精度模数转换器芯片

由于阻性输入阻抗和自带抗混叠滤波特性,连续时间ΔΣ调制器(CT-DSM)在无线收发机领域得到广泛应用。与单环路架构相比,多级噪声整形(MASH)架构通过级联多个低阶单环路,实现更好的稳定性,从而允许提升最大稳定输入幅度。然而,其固有的量化噪声泄漏会显著降低CT MASH DSM在PVT下的鲁棒性,无论通过模拟域的电路优化技术或者数字域的校准技术,都会极大地降低系统能效。

面对MASH存在的量化噪声泄露问题,BiCASL团队提出了新型的流水线型MASH架构,1)第一级不再像传统MASH架构一样,直接从量化器提取量化误差,而是从第一级的DSM环路提取误差信号;2)第二级DSM环路采用纯前馈式架构,实现特殊的信号传递函数;3)移除数字滤波器,两级输出直接相减形成MASH架构的最终输出。该架构不再尝试消除第一级的量化误差,而是通过不同阶数的噪声整形函数同时压制不同环路的量化误差,进而极大地提高了MASH架构自身的鲁棒性以及功耗效率。

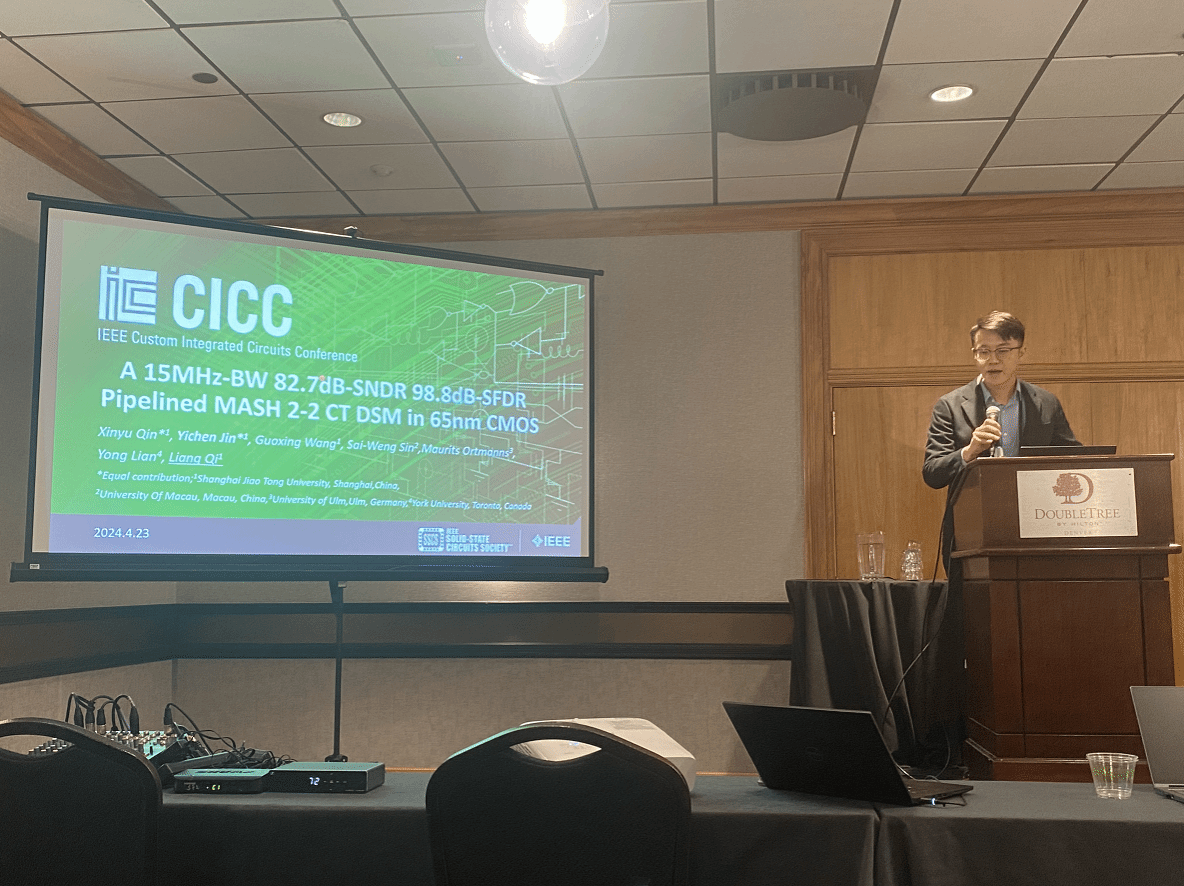

基于上述创新设计,课题组研制了一款基于65 nm CMOS工艺的宽带高精度、高线性度连续时间2-2 MASH CT DSM芯片,并对芯片进行了性能测试与汇报。在15MHz带宽下,通过片内的DAC失配后台校准,可以实现82.7dB SNDR,98.8dB SFDR,功耗仅为16.9mW,Schrier 品质因子达到172.2dB,该品质因子在先进宽带MASH工作中占据着领先位置。

该工作以《A 15MHz-BW 82.7dB-SNDR 98.8dB-SFDR Pipelined MASH 2-2 CT DSM in 65nm CMOS》为题,发表于今年CICC,文章的第一作者是上海交通大学微纳电子学系硕士生秦新宇(2020级,已毕业)和博士生金逸辰(2024级),祁亮副教授是该文章的通讯作者。

图1 现场汇报照片

图2 高精度宽带CT-DSM显微照片

2. 生理信号采集前端芯片

在ExG信号记录过程中,由运动,环境干扰以及电刺激产生的伪影干扰可表现为共模、差模以及两者的混合形式,并且其幅度可高达几百mV。为了减小这些伪影并最大限度地减少信息损失,传感器接口面临高输入范围和快速响应速度的挑战。相比于牺牲能耗的高动态范围的ADC方案,当前研究集中于伪影恢复架构研究以兼顾能耗和响应速度。然而当前研究受限于信号路径中积分器的有限带宽、量化器延时和伪影检测反馈延时,伪影恢复速度仍有较大提升空间。

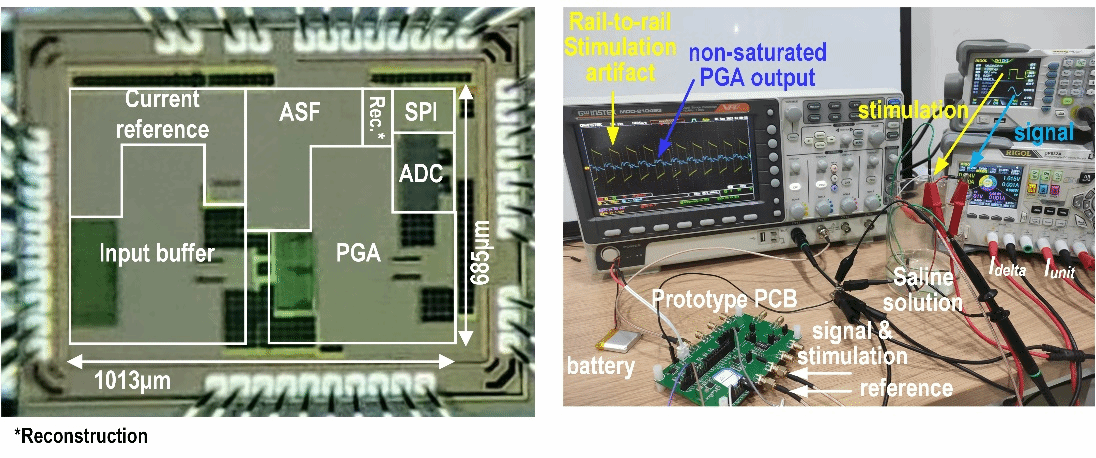

BiCASL团队从伪影恢复架构入手,首次提出了基于连续时间跟踪和缩放的快速伪影恢复技术。该技术利用通过将输入信号异步折叠到一个恒定的阈值窗口来处理大的伪影事件同时提升响应速度,接着对折叠后的信号进行放大进一步提高信号分辨率。首先通过AC耦合的输入缓冲器,处理共模干扰以及电极直流失调;接着通过嵌入输入电平移位器的比较器实现阈值窗口设置和连续时间跟踪;然后通过另一个电平移位器和电流DAC实现输入信号在电流域的折叠;在大幅度伪影刺激下,该架构的响应速度仅取决于比较器触发延时和异步逻辑控制延时,从而大幅缩短了伪影恢复时间。接着折叠后信号的经过PGA放大后,再被SAR ADC量化,最终可在数字域重构原始信号。

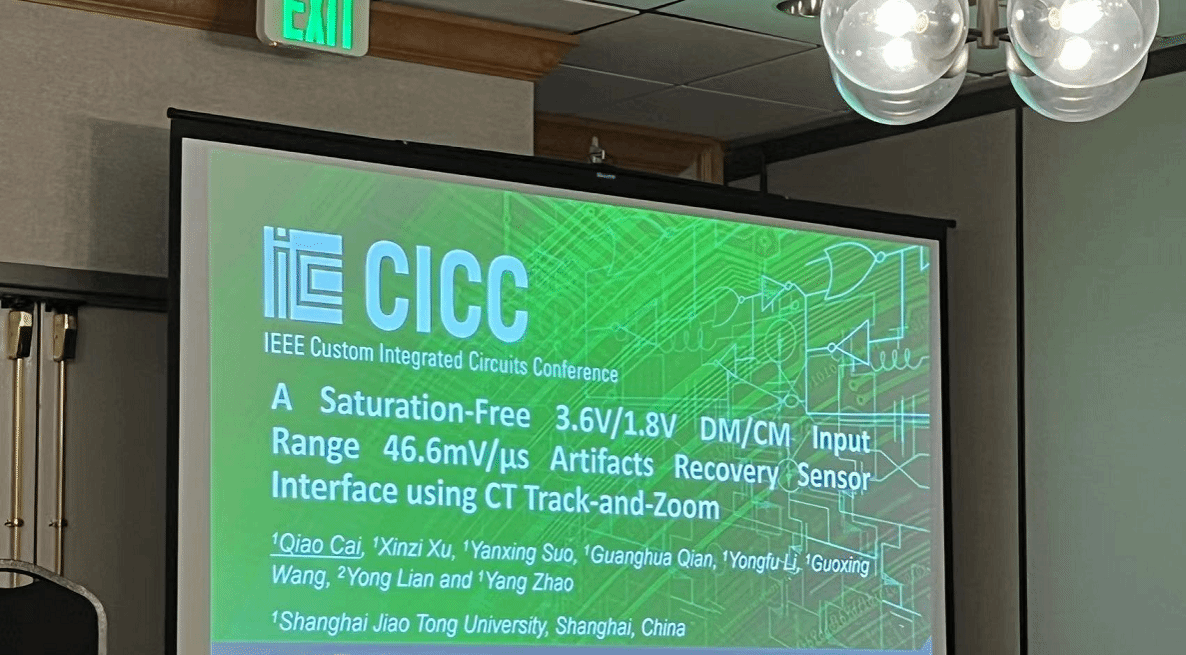

基于上述创新设计,课题组在CMOS 180nm工艺下实现了一个无饱和生理信号采集前端,输入范围达到3.6V/1.8V(共模/差模),伪影恢复速度为46.6mV/μs,比现有技术分别大2倍以上、快3倍以上。

该工作以《A Saturation-Free 3.6V/1.8V DM/CM Input Range 46.6mV/μs Artifacts Recovery Sensor Interface using CT Track-and-Zoom》为题,发表于今年CICC。2020级博士研究生蔡桥为该论文的第一作者,赵阳副研究员为通讯作者。

图3 现场汇报照片

图4 芯片显微图和体外刺激伪影恢复测试

关于CICC:

在集成电路设计领域,IEEE固态电路协会(Solid-State Circuits Society)主办的定制集成电路会议(CICC)是IC设计领域顶级会议之一,以论文录用率低、作品创新性和实用性强著称,每年吸引全球范围内大量学术界、工业界研发人员的关注和参与。会议内容涉及模拟电路设计、生物医学、传感器、显示器和MEMS,数字和混合信号SoC/ASIC/SIP, 嵌入式存储器件等方面,重点讨论如何解决集成电路设计问题的方法,以提高芯片各项性能指标。