近日,上海交通大学生物电路与系统实验室(BiCASL)在脑机接口神经记录前端芯片领域取得重要进展。在 IEEE Journal of Solid-State Circuits(JSSC)上发表题为“PWM-Based Impedance Boosting Technique With Autonomous Background Calibration for VCO-Based Neural Front Ends”的研究成果,首次报道了基于PWM脉宽调制的输入阻抗后台校准方法,并实现了融合模数转换和数字域阻抗调制的高能效、小面积神经记录前端传感电路。论文链接https://ieeexplore.ieee.org/document/10890975

研究背景

脑机接口是近年来国内外研究热点,是未来产业的代表领域之一。电容耦合型传感电路具有能效高、电极失调抑制强,能够抵抗神经调控干扰电压等优点,在高通量神经传感系统中得到了广泛应用,但是输入阻抗受耦合电容限制较低。传统前台阻抗校准技术可以将输入阻抗校准提升到较高的值,但是需要输入特定类型的信号,整体系统较为复杂,难以实现高精度和高速度的阻抗校准。

研究内容

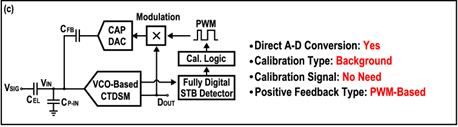

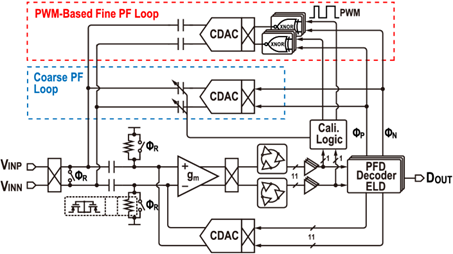

基于PWM调制后台自适应阻抗校准技术无需前台校准信号,可实现自适应后台校准

融合数模转换和脉宽调制校准的数字化神经传感前端接口电路

针对目前输入阻抗自校准技术的不足,本论文提出基于PWM脉宽调制的输入阻抗后台校准方法,并且将此技术应用到具有高动态范围的基于VCO 的CTDSM 前端电路中,利用PWM 波调制的方式精细调节正反馈强度,通过将PWM频率和采样率设为一致,PWM的谐波将被CTDSM的自身抗混叠特性完美滤除,无需额外的低通滤波电路,同时此方案无需复杂的正反馈电容阵列和极小的单位电容。此外,本论文充分利用了基于VCO的CTDSM与锁相环的相似性,提出在后台检测锁相环失锁的方法,进而能够用很低的硬件和功耗开销在数字域为阻抗自校准算法提供稳定性判据。

研究成果

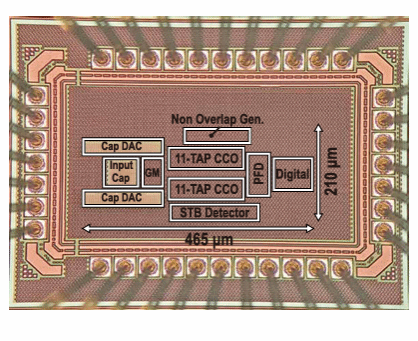

180nm工艺流片芯片显微照片

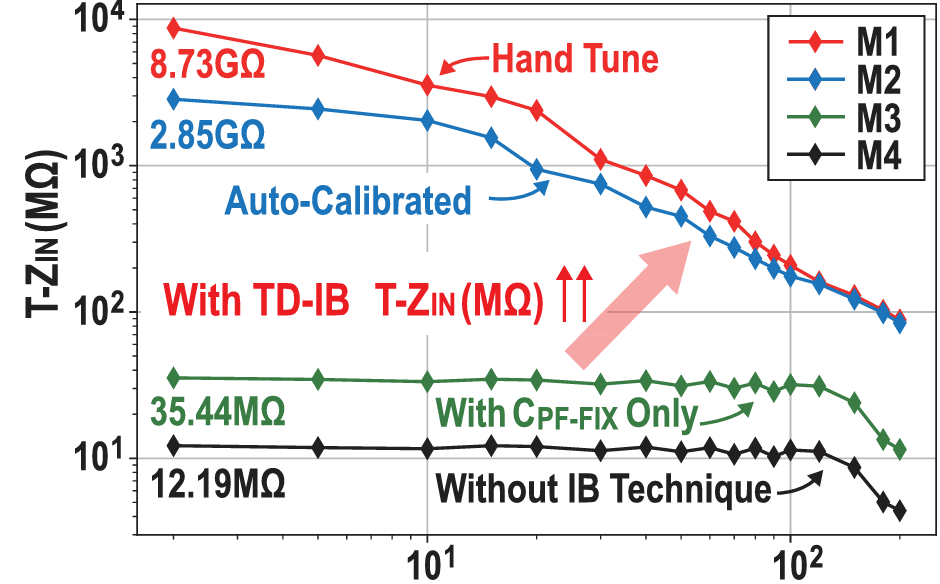

无阻抗提升电路(黑色)、传统阻抗提升电路(绿色)、手动调整PWM调制和自动PWM调制阻抗提升电路中的不同输入阻抗提升效果

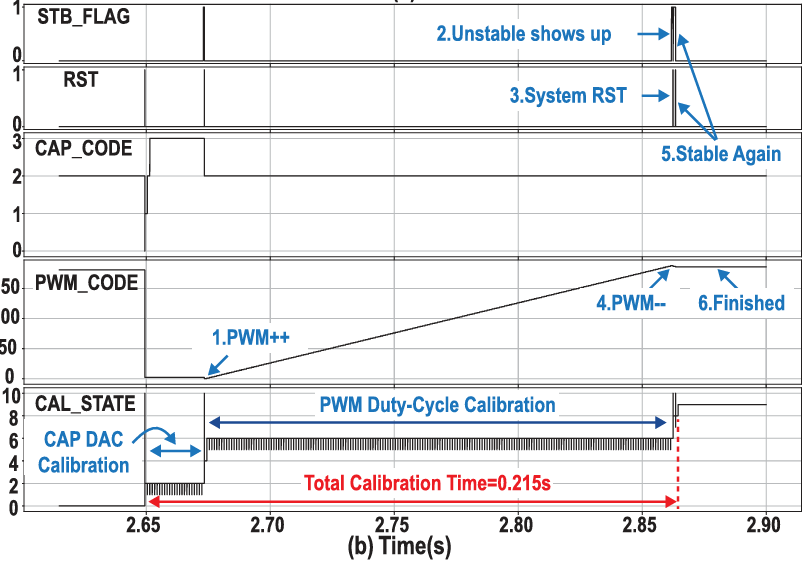

自适应阻抗提升校准和提升的收敛时间小于0.25秒

芯片采用180nm 标准CMOS工艺流片,本芯片基于高动态范围CTDSM 前端电路,首次实现了无校准信号的后台阻抗自校准,并且将校准收敛时间降低到0.215秒,达到文献报道最快水平;单通道传感电路包含数模转换模块功耗小于27微瓦,面积小于0.1平方毫米。本论文提出的创新技术为阻抗提升技术低成本的集成到大规模多通道脑机接口系统奠定了基础。

论文作者信息

论文第一作者为集成电路学院已毕业博士生刘怀宇,通讯作者为刘彦副教授,共同作者为博士生林阳,邢铺嘉和王国兴教授。

关于IEEE固态电路期刊

IEEE固态电路期刊(JSSC)是国际集成电路领域最高级别期刊之一,旨在发布集成电路设计领域最新进展和里程碑成果,代表业内顶尖技术水平。